本文要點:

1. 寄生電容的定義

2. 電路中寄生電容的來源

3. 測量和分析寄生電容的方法

4. 如何減少寄生電容的影響

一、定義

寄生電容是一種現(xiàn)象,即電路中的元件在物理上不是電容時表現(xiàn)得像電容。

含義:原本沒有在那個地方設計電容,但由于布線之間總是有互容,互容就好像是寄生在布線之間的一樣,所以叫寄生電容,又稱雜散電容。(官方解釋)

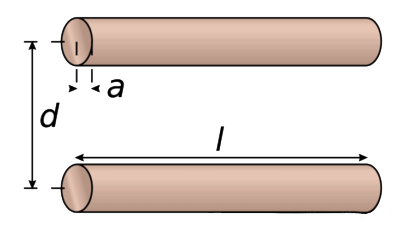

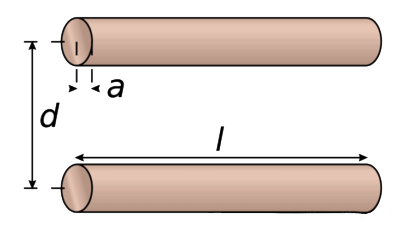

寄生電容本身不是電容,根據(jù)電容的原理:電容一般由兩個極板和絕緣介質構成。因此寄生電容無法避免的。

(導體間寄生電容是面積與距離的關系)

由此我們能夠得知,它是由于電子元器件的結構、材料等因素導致的,因此寄生電容無法避免的。同時,寄生電容的存在會對電路的性能產生影響。

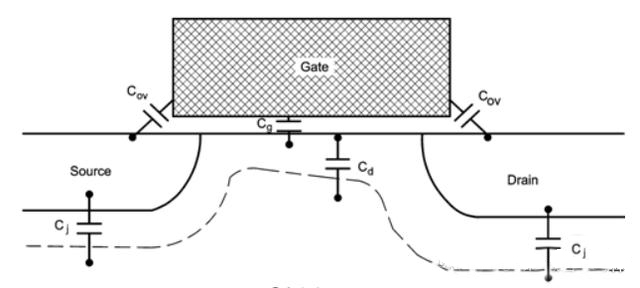

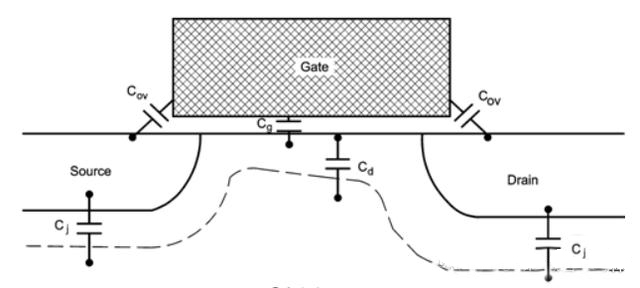

二、電路中的寄生電容

寄生電容在電路中時常出現(xiàn),一般來源于以下幾個方面:

a. 元件之間的電容(不同元件之間的導線、引腳等產生的)

b. 元件與地之間的電容(元件與地之間的導線、引腳等產生)

c. PCB板上的電容(不同導線之間、導線與地之間形成)

d. 其他因素(電磁干擾、溫度變化等產生)

在電路中,寄生電容會導致信號的衰減和相位移動,從而影響其的性能和穩(wěn)定性。

特別是在高頻電路中更為明顯,在高頻電路中,寄生電容會導致信號的失真和噪聲的增加。

三、測量和分析寄生電容的方法主要有:

- 使用LCR表進行測量;

- 使用示波器和信號發(fā)生器進行測量;

- 使用頻率響應分析器

(以上方法都存在一定的誤差風險,實際應用需要進行校準和誤差分析。)

四、如何減少寄生電容

為此我們需要采取一些措施來減小寄生電容的影響:

1. 盡可能縮短元件之間的距離,從而減小元件之間的電容。

2. 將元件引腳與地之間的距離盡量縮短,減小元件與地之間的電容。

3. 合適的PCB布局,有效減小PCB板上的電容。

4. 采用屏蔽措施,以便減小電磁干擾。

此外,我們還可以利用補償電路,例如使用電容器和電感器來抵消寄生電容的影響,還可以使用高速緩存和其他優(yōu)化技術來提高系統(tǒng)的性能和穩(wěn)定性。

(寄生電容)

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯(lián)系號碼:18923864027(同微信)

QQ:709211280